使用锁相放大器进行模拟信号的捕获和跟踪

相关产品 MFLI HF2LI UHFLI GHFLI SHFLI

介绍

模拟信号的锁相环(PLL)在当今的物理和工程应用中无处不在。本白皮书介绍了它们的基本功能和工作原理。它还涵盖了几个可以方便的使用苏黎世仪器的锁相放大器的实际用例。

历史上,最早的PLL系统被提议用于调幅(AM)信号的接收,以利用零差检测并避免由超外差接收引起的镜频响应[1]。为了正确接收,零差检测器要求接收信号的本振(LO)频率等于接收信号的载波频率,LO相位也需跟随接收信号载波的相位。设计PLL电路以将LO相位锁定到载波相位,并确保两个信号之间的恒定或时不变相位关系。

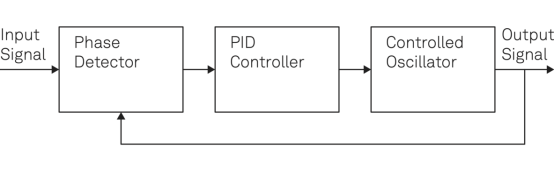

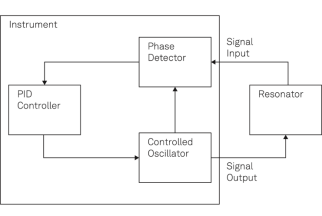

PLL是一种具有负反馈的闭环控制系统,在两个周期性信号之间保持明确的相位关系:其输入作为参考,输出跟随。作为锁相的结果,这两个信号具有相同的频率,这使得能够在多个信号源上产生和输入信号相干的信号。在其简化形式中,PLL由以下组成模块组成[2]:

1. 相位检测器

2. PID控制器

3. 受控振荡器

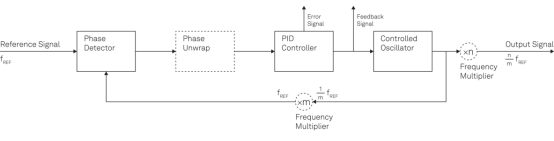

如图1所示,PLL接收输入信号,并将其相位转移到受控振荡器,以生成跟随输入信号相位的输出信号。

相位检测器单元测量两个信号之间的相位差。然后将相位检测的结果与相位设定点进行比较,以产生用于比例积分微分(PID)控制器的误差信号。基于误差信号,PID控制器产生反馈信号以调谐受控振荡器的频率。这样,受控振荡器跟随输入信号相位,从而产生与输入信号频率相同的信号。

在对PLL组成模块进行更详细的叙述之后,进一步描述了典型的PLL应用,并强调了基于图1中的基本PLL方案后具体实现中的差异。我们还提供了关于设置PLL、选择其关键参数以及表征和优化其性能的实用提示。在白皮书的最后,我们简要介绍了PLL系统的不同噪声特性和模型。

图1:PLL的原理图,显示了其基本构成模块。PLL产生跟随输入信号的相位和频率的输出信号。它是使用负反馈闭环来实现的。

PLL组成模块

PLL系统可用于根据不同应用处理模拟或数字信号。本文讨论在研发实验中用于处理模拟信号的数字PLL。我们研究了通过数字信号处理实现相位检测器、PID控制器和受控振荡器的情况。

相位检测器

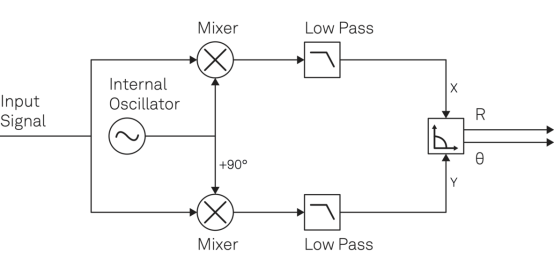

相位检测器将两个周期性信号作为输入,并产生与两个输入信号之间的相对相位差成比例的输出信号。根据信号类型采用不同的技术来实现相位检测。例如,当处理数字系统中使用的方波时,相位检测器由XOR门和低通滤波器提供[3]。更通用的是使用双相位解调器测量一个输入相对于另一个输入的同相分量X和正交分量Y来获得相位差,如图2所示。

图2:使用锁相放大器的双相位解调进行相位检测。同相分量X和正交分量Y由两个独立的信号路径生成,以导出输入信号的相对相位θ和信号幅度R。

实现双相位解调的最常见的仪器之一是锁相放大器。它们的嵌入式可调低通滤波器提供了额外的降噪优势和调谐PLL带宽的能力,见图2。低通滤波器可以滤掉施加到PID控制器上的不期望的频谱分量和噪声。这些滤波器的截止频率和相位延迟影响了整个PLL带宽的上限。《锁相放大器原理》[4]中提供了低通滤波器及其对信噪比(SNR)和测量速度的影响的更详细描述。

使用锁相放大器进行相位检测的另一个优点是锁相放大器还测量信号幅度。这可以用于其他控制,如[5]中所述的自动增益控制(AGC)。通过从笛卡尔坐标变换到极坐标,可以很容易地从测量的同相X和正交Y导出振幅R和相位θ:

(1)

(1)

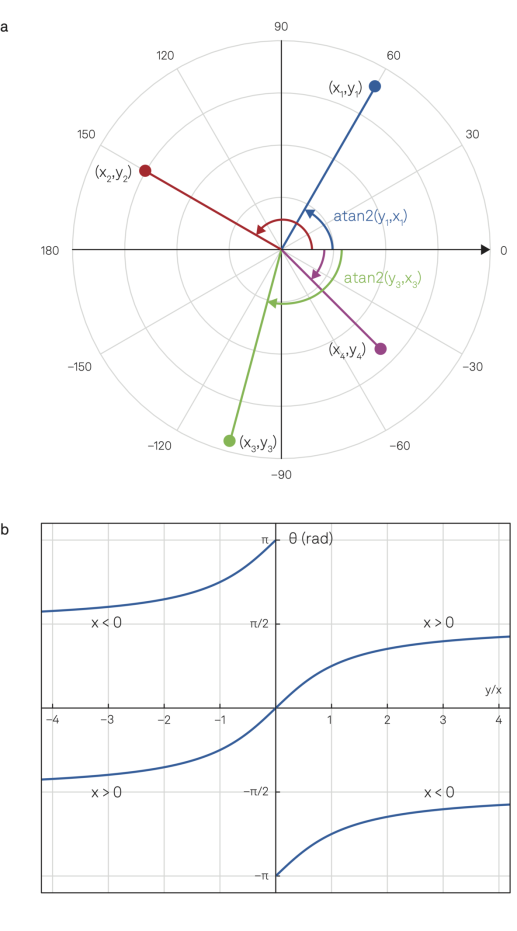

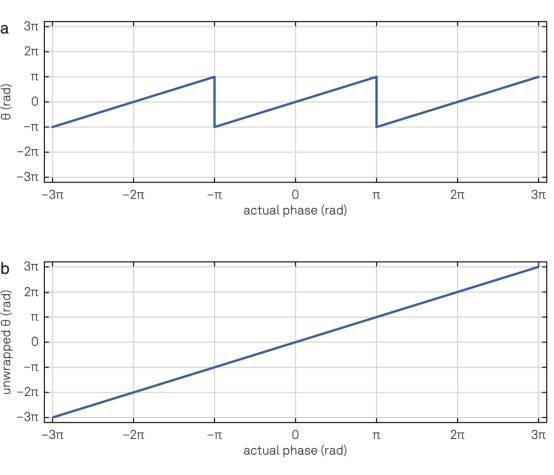

使用“atan2”函数而不是“atan”可确保相位角覆盖相位圆的所有4个象限,即(-π,π),这取决于图3中绘制的正交分量的符号。

当相位信号与系统的采样率相比变化足够慢时,可以在数字域中容易地检测和解决交叉象限时所经历的不连续性。该函数被称为“相位展开”,并将相位值的可用空间增加到原始间隔的许多倍,如图4的面板所示。苏黎世仪器公司的锁相放大器支持高达±1024π的相位捕获范围,例如,当在多个波长的距离上稳定光学干涉仪时,这是必需的[6]。

特别是,苏黎世仪器公司的PLL,现场可编程门阵列(FPGA)分别通过模数转换器(ADC)和数模转换器(DAC)与模拟输入和输出信号连接。

图3:(a) 极坐标表示信号分量对(x,y)的相位,覆盖范围从-180°到+180°,由atan2(y,x)表示。(b) 根据x的符号,atan2(y,x)是一个双值函数,与返回点(x,y)的直线与正x轴之间的角度的比值y/x有关。

图4:(a) 通过用作相位检测器的锁相放大器测量的相位。(b) 显示实际相位和测量相位之间的线性关系的未缠绕相位。

PID控制器

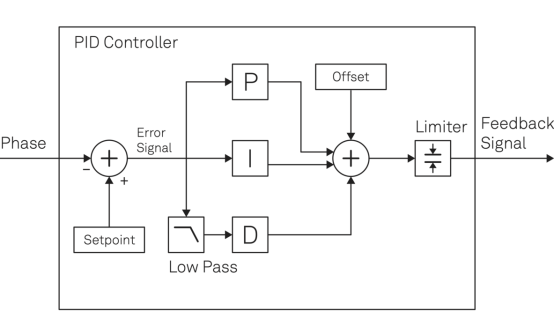

PID控制器从相位检测器接收相位差信号,并与用户定义的设定点相减以产生误差信号e(t)。然后,通过应用比例、积分和微分运算,从误差信号中生成对受控振荡器的反馈,如图5所示。因此,最终反馈信号u(t)由以下表达式给出:

![]() (2)

(2)

其中是K0偏移值,Kp、Ki和Kd分别是P、I和D系数。在很多实际应用中,使用比例P和积分I即可得到足够好的执行和稳定过程,也可以添加导数项以进一步减小误差信号离零的平均偏差。然而,这也会增强误差信号的高频分量从而给环路引入不稳定性。额外的低通滤波器可以通过抑制较高频率的增益来抑制环路的不稳定性。PLL的速度与闭环系统的带宽有关。当涉及到调整环路带宽时,需考虑以下几点:

1. 最小化误差信号离零的平均偏差通常需要优化PID参数以最大程度提高反馈带宽和增益。这通常在很少自发干扰的情况下有效。这样的设置通常可使稳定时间接近其最小值。苏黎世仪器PLL具有自动调谐功能,使用户更容易找到最佳工作点。

2. 闭环操作的高稳定性和大捕获范围有时比误差信号离零的平均偏差更重要。这种对不同类型的外部扰动的鲁棒性有时是通过故意使用较弱和较慢的反馈信号来实现的,从而减少过度反应并避免失控。当初始条件没有完全满足时,这种选择通常伴随着环路滤波器的更稳健的启动。不幸的是,最佳设置在很大程度上取决于设置的具体情况,需要手动调整。

图5:PID控制器的示意图:从可调相位设定点减去来自相位检测器的相位信号,然后结果通过三个不同的支路P、I和D,然后将结果信号添加到偏移。限制器有助于将范围限制在有用的参数空间内。

3. 由于只有环路滤波器带宽内的输入信号的噪声分量被传输到受控振荡器,因此有时需要设置明确定义的滤波器带宽。良好设计的低通滤波,可以避免不需要的频率分量对输出信号的泄漏。苏黎世仪器PLL配有PID Advisor,可以对环路中涉及的所有组件进行建模,并帮助用户快速识别和设置所需的带宽。

一个具有高度实际相关性的附加功能是可调节的输出偏移,可以从PID控制器输出的默认位置开始,这样当回路打开时,用户可以从一个良好的起点中获益。此外,设置反馈信号的上限和下限可以将控制操作限制在用户定义的频率范围内。当输入信号包含多个不同的频率分量,但只需要跟踪特定的频率分量时,或者当需要避免对外部设备的损坏时,设置这样的限制特别有用。

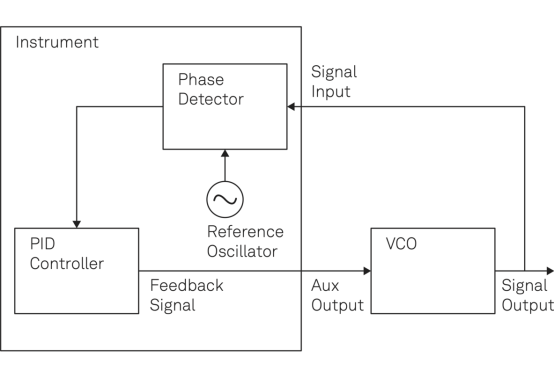

振荡器和频率参考

PLL中的受控振荡器通常由压控振荡器(VCO)或数控振荡器(NCO)实现,其频率可以分别通过模拟和数字反馈进行调谐[7]。VCO主要用作外部控制振荡器,它们是广泛使用的有源组件,输出具有固定振幅的正弦信号,同时可以使用模拟输入电压在一定范围内调整它们的频率。VCO的主要特性是其频率随控制电压的变化而变化,理想情况下,控制电压与输出频率变化呈线性关系。与VCO相比,NCO可以确保线性,并且可以在任何给定时间响应数字形式的频率值。当然有更多的方法来产生可控的周期性信号。然而,追根究底大多都可以追溯到上面两个例子中的一个。例如,激光束和频率梳之间的拍音通常在光电二极管的输出端产生射频信号。当将反馈信号施加到激光器的调制输入时,其光学频率将根据电压信号而改变,因此,光电二极管检测到的频率将改变。忽略所有涉及的光信号,这是一种与使用VCO非常相似的配置,例如,它可以用于建立用于激光频率稳定的光学PLL。

当使用苏黎世仪器公司的锁相放大器时,相位检测器的一个输入始终来自内部数字振荡器。在FPGA上实现的这些NCO的频率可以通过数字设置频率值来调整,同时确保相位连续。NCO频率可以改变的最大速率由FPGA时钟速度或频率寄存器更新速率给出。该速率远高于可实现的最大控制环路带宽。

如果NCO跟随外部频率参考,则PID控制器对内部NCO的频率进行数字调节,以跟踪参考信号。然而,如果内部振荡器为外部VCO提供频率参考,则其频率固定在特定值,同时PID控制器应用反馈信号来调整外部VCO的频率。在需要锁定两个外部源的情况下,必须设置两个PLL,并将一个联合内部NCO用作中间项。

值得一提的是,在宽频率范围内准确和精确的周期性信号生成对于各种测试和测量(T&M)应用至关重要。许多覆盖宽频率范围的T&M仪器使用基于PLL的频率合成来生成频率可调的周期性信号。为了将宽范围和精确频率生成的灵活性与高稳定性和准确性相结合,PLL可以将高精度和低相位晶体振荡器(如恒温晶振(OCXO))的最佳性能与受控振荡器(如VCO)的灵活性相结合。为此,PLL将受控振荡器频率f与用作参考的OCXO频率fREF的小数倍频同步。

通过使系数因子可调,可以获得根据f=(m/n)fREF的宽频率范围,见图6。振荡器频率现在可以通过调节比值m/n来广泛调谐,同时OCXO频率固定。例如,在许多T&M仪器中为10MHz或100MHz。除了频率精度和稳定性之外,PLL的实现细节还影响其他因素,如相位噪声、杂散边带和锁定时间,这些因素决定了生成信号的质量,从而影响了部署这种频率合成的系统的性能。对于大多数数字信号处理仪器来说,这一功能是内置的,因此内部NCO的信号可以作为可靠的频率参考。

应用

锁相环的主要功能是由两个振荡器表示的两个系统的时基同步。存在许多需要同步两个或多个振荡信号的应用。虽然PLL广泛用于数字系统中,如减少抖动、偏斜抑制、频率合成和时钟恢复,但这里我们重点关注PLL在模拟信号中的应用,特别是属于以下三种配置之一的PLL:

1. 频率跟踪:PLL将外部源映射到内部振荡器,见图6。

2. 谐振驱动:PLL驱动设备的时变谐振,见图9。

3. 振荡器控制:PLL向外部变频源提供模拟反馈,见图10。

频率跟踪

使用锁相放大器的广泛应用中需要用到相干信号检测,即需要信号源和信号检测器的同步。如图6所示,在其最常见的形式中,频率跟踪系统接收外部参考信号,并将其频率映射到系统的内部振荡器。该应用的一个具体例子是通过具有外部参考的锁相放大器进行的零差检测。为了正确地恢复输入信号的幅度和相位,锁相放大器需要来自信号发生器的外部参考信号,该信号发生器决定测量频率,例如,光学斩波器。锁相放大器然后需要将其内部振荡器锁定到该外部参考频率,以相干地检测感兴趣的接收信号。这通常通过类似于图6的PLL配置来完成。对于大多数使用情况,通常自动找到PLL的正确中心频率和带宽。然而,当给定特定的带宽要求或频谱包含多个分量时,可能需要调整各个PLL设置以确保准确的频率跟踪。此外,通过使用定义的带宽将外部参考信号映射到内部振荡器,会在跟踪频率下产生无抖动和无杂散的信号。这一方面对于需要频谱滤波的应用是有益的,其中可以选择小的闭环带宽来排除或抑制外部信号或噪声源。

全数字实现的另一个优点是在不损失任何信号质量的情况下,可以对被跟踪的频率进行乘法或除法,以产生谐波和比率的内部参考。使用参考频率的分数倍进行解调能够实现基于相同外部参考的额外测量方案,例如,具有谐波叶轮的光学斩波。

图6中PLL配置的另一个重要应用是载波恢复。传输系统中接收信号的相干解调要求接收器知道载波的频率。然而,由于发射机和接收机之间的距离,它们不能共享相同的时钟源,因此除非接收机使用PLL锁定到发射机发送的载波,否则无法实现完美的同步。除了调制信号之外,许多通信系统还发送纯音作为接收机的PLL可以锁定的导频。如果没有PLL单元的载波恢复,在大多数收发器系统中就无法实现相干通信。在没有发送导频或调制信号被载波抑制的情况下,使用稍微修改的PLL配置,例如Costas环路,来提取载波频率[8]。类似地,对于锁相放大器,当没有外部参考可用时,可能会根据信号质量将内部振荡器锁定到测量信号本身。这种所谓的锁相放大器的“自动参考”配置只能提取信号的振幅信息,而不能提取相位。

图6:原理图显示了PLL的组成模块,该PLL具有用于相位展开和分数频率锁定的扩展功能。除了输出信号之外,许多应用还受益于诸如误差和反馈信号的中间信号。

频率提取、滤波和计数

类似于上面的例子,PLL还可以从拥有多个不同频率的信号中提取特定的频率分量。这种提取需要在PLL启动时将可变源调谐到接近期望频率,以将正确的频谱分量传输到PLL内部振荡器。这种方法非常强大和灵活,可以过滤出特定的频谱分量,跟踪它们,并在设置的其他部分将它们作为纯信号重复使用。考虑到对内部NCO的反馈是数字的,可以高速跟踪和记录瞬时频率,从而提供额外的频率计数器功能。

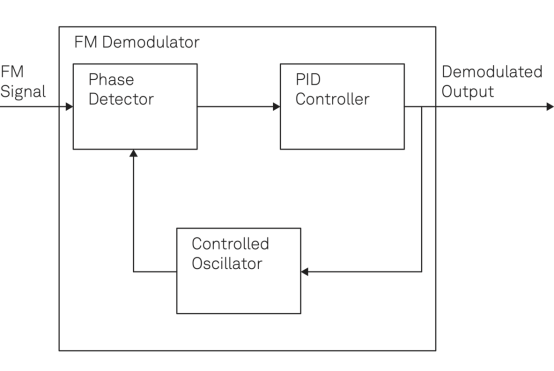

调频解调

调频(FM)是一种将消息信号的信息编码为载波频率的技术。在调频系统中,载波的瞬时频率跟随消息信号变化。因此,需要频率跟踪器来解调载波并从载波频率中提取消息。在调频系统的解调方法中,PLL以低失真和对幅度噪声的敏感性低而脱颖而出。

如图7所示,基于PLL的FM解调器相对简单,不需要改变基本的PLL配置。当没有对载波施加调制时,施加到受控振荡器的反馈信号处于其产生载波频率范围的中间。然而,如果调制改变了载波频率,则环路滤波器改变施加到振荡器的反馈电压以改变其频率。这样,闭环保持锁定,即振荡器信号跟随接收到的FM信号的相位。可以看出,施加到受控振荡器的反馈信号与接收到的载波的频率变化成比例。因此,解调后的信号可以被放大并传送到下一级进行采集和处理。

图7:基于PLL的FM解调器的示意图,其中解调的输出与施加到受控振荡器的反馈信号成比例。

在设计基于PLL的FM解调器时,主要考虑的是由PLL的闭环带宽确定的解调带宽。解调带宽决定了信号带宽,从而决定了每次可以在通信信道上传输的最大信息量。因此,相位检测器和PID控制器必须足够快以覆盖FM信号所需的带宽。此外,使用具有高度线性响应的振荡器对于最小化解调信号的失真并保持解调过程尽可能线性至关重要。换句话说,当使用VCO作为受控振荡器时,电压-频率曲线需要在接收到的FM信号的频率范围内尽可能线性。

共振驱动

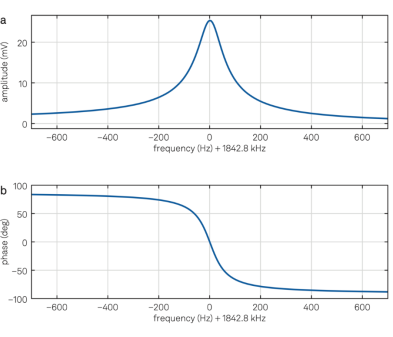

在许多应用中,如原子力显微镜(AFM)和微纳机电系统(MEMS/NEMS),驱动具有受控相位和频率的器件是很重要的。在这种应用中,系统的一部分表现得像具有洛伦兹形状振幅传递函数和S形相位演变的谐振器,类似于图8,示出了谐振频率为1.84 MHz的谐振器的波特幅度和相位图。通过在共振处驱动装置,可以从共振增强和测量响应的线性化中受益。通常,这种系统的谐振频率随着一些物理量(如温度、力等)而变化。因此,为了以固定相位驱动谐振器,需要根据环境参数引起的谐振频率变化来调整信号频率。以谐振器的输出相位保持在用户定义的设定点的方式控制驱动频率的PLL能够实现这种谐振驱动。图9示出了PLL控制的谐振器驱动器的框图,其中振荡器提供谐振器的驱动信号和相位检测器的参考信号。PLL确保设备在相同的工作点连续驱动,即使其谐振频率随时间变化。

图8:(a) 苏黎世仪器公司锁相放大器的频率响应分析仪测量的晶体谐振器的波特幅度和(b)相位图。

PID控制器将相位检测器输出处的误差信号转换为振荡器输入处的控制信号,以根据谐振器响应的变化来调整信号频率。

例如,原子力显微镜的悬臂头包括一个音叉谐振器,它利用其谐振频率中的诱导位移来测量被测样品表面所施加的力场。为了测量这种频移,从而表征表面形貌,需要一个PLL来锁定悬臂梁的共振。PLL误差信号随后将表示表面形貌。另一个典型的例子是惯性测量系统,如MEMS陀螺仪和加速度计[5]。至关重要的是,无论观察到的旋转运动如何,都要在共振时驱动这样一个系统的振动质量。由于旋转会改变共振频率,因此PLL对于传感器在其变化的共振频率下的稳定驱动至关重要。PLL在控制谐振系统中的这种应用包括更多的例子,例如泵浦探针、离子捕获和参数反馈冷却实验,其中PLL被修改以适应特定应用的要求。一个例子是在参数反馈冷却中以谐振频率的二次谐波对系统进行异相驱动[9]。

图9:通过PLL对谐振器进行闭环控制的示意图。谐振器与仪器一起形成PLL系统,其中受控振荡器通过保持相对相位恒定来跟随变化的谐振频率。

振荡器控制

如前所述,为了简单起见,我们将要控制的任何外部振荡器建模为VCO。在图10所示的PLL配置中,内部振荡器为相位检测器提供参考信号,用于测量外部振荡器相对于参考的相位。PID控制器将测量的相位差转换为反馈信号,并将其应用于外部VCO以调整其输出频率。通过这种方式,可以将稳定的内部NCO的时基内容映射到外部系统。相位检测器的频谱滤波以及模拟电压信号的可编程输出限制器有助于在所需频率下的稳定操作,即使在锁定丢失的情况下重新锁定之后也是如此。此外,即使积分器进入饱和状态,系统也不会在定义的安全区之外的任何值下驱动,在该安全区内可以保证可靠的操作。

图10:使用锁相环基于参考振荡器来控制VCO的频率。

启动PLL

以下步骤提供了一种成功闭合反馈回路并使PLL工作的系统方法:

1. 获得系统的开环响应。

2. 找到一组粗略而保守的PID参数来启动循环。

3. 调整PID参数以优化SNR、速度或鲁棒性。

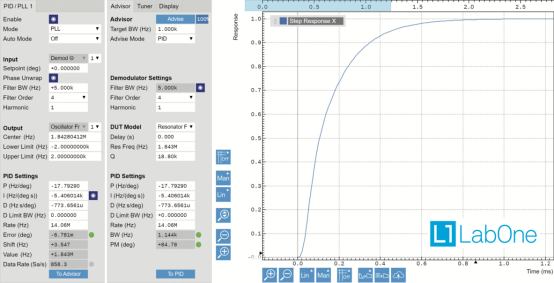

找到合适的PID参数和启动条件的初始集合可能很棘手。是苏黎世仪器公司与仪器硬件接口的控制软件,为所有3个步骤提供了有效的工具,使启动和优化PLL的过程尽可能高效和简单。作为第一步,需要获得被测器件(DUT)的开环响应。这可以是谐振器的频谱响应,也可以是显示频率相对于VCO的调谐电压的曲线。LabOne的扫频器模块提供了获得系统开环响应所需的所有成分,因为它可以扫频所施加信号的频率、相位、振幅和偏移,并获取测量结果。此外,曲线拟合、跟踪、峰谷查找等集成数学工具有助于用户提取正确PID控制所需的系统特性,如品质因数、增益和斜率。

一旦已知系统响应,就可以通过考虑在相位检测器单元中使用的低通滤波器的特性以及在各个点引入的系统延迟来设置特定的目标带宽。

方便的是,LabOne提供了一种PID顾问,该顾问采用优化算法来调整PID控制器,并确定给定目标PLL带宽所需的滤波器设置。PID Advisor会考虑硬件的所有物理延迟和增益。此外,它还采用了各种数学模型来考虑所附设备的传递函数。在选择设备配置后,无论是内部PLL、外部谐振器还是VCO型配置,Advisor都会运行其算法来计算P、I和D参数,并获得滤波器特性以及相位裕度和实际带宽。它还显示了各种时间和频谱图,如波特幅度和相位图,以及整个系统各个入口点的阶跃响应,说明了设计的PLL工作的速度和稳定性。

将PID Advisor获得的PID设置应用于仪器并启用PID控制器应能成功闭环PLL。使用LabOne的绘图工具,可以连续监测PID误差和输出信号,同时调整PID设置,观察其对PLL性能的影响。除了手动调整PID参数外,LabOne中提供的PID控制器的自动调谐功能还可以自动修改PID设置,以提高PLL性能。图11显示了LabOne用户界面的PID/PLL选项卡,其中在用户友好的web环境中提供了设计、优化和运行PLL所需的所有工具。

图11:LabOne用户界面的PLL/PID控制器选项卡显示输入、输出、相位展开和PID参数(左)、PID顾问、调谐器和DUT模型(中)以及最终闭环系统的阶跃响应(右)。

PLL中的噪声

PLL的模拟输出是正弦信号,该正弦信号具有固定的幅度但跟随设定点或参考信号而变化的频率和相位。在具有固定设置点的理想PLL中,输出信号的频率和相位应该是时不变的。然而,由于实际系统中的噪声,PLL受到相位和频率波动的影响。相位波动可以通过标准偏差为σφ的零均值随机过程φ(t)来建模。因此,具有固定设定点的PLL的输出由以下正弦信号给出,载波频率fc为Hz,相位ψ为rad:

![]() (3)

(3)

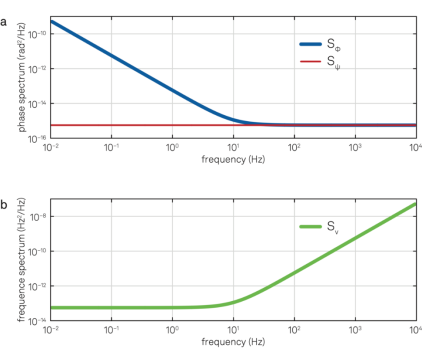

其中A是固定幅度。相位噪声最好用其功率谱密度(PSD)来表示,功率谱密度由Sφ(f)表示,这是通过 φ(t)从的自相关中进行傅立叶变换来获得的。相位噪声PSD示出在远离载波频率fc的偏移频率f处在1Hz的单位带宽中存在多少噪声功率。其单位为rad2/Hz;然而,在许多应用中,它也以dBc/Hz表示,这与载波功率有关。在这里,我们将解释如何用不同的单位来表示相位噪声。IEEE标准[10]将中的rad2/Hz作为相位的单侧(双边带或DSB)频谱密度,并引入双侧(单边带或SSB)频谱强度Lφ(f) 作为以dBc/Hz表示相位噪声的标准方式:

![]() (4)

(4)

因此,数据表中提供的相位噪声PSD总是比实际单侧频谱低3dB;在基于频谱密度计算噪声功率和时间抖动时应当小心。

换言之,测量带宽δf内的相位噪声功率σφ2 ,用rad2表示,通过这两个积分中的任意一个获得:

![]() (5)

(5)

例如,在某一偏移频率附近具有−120 dBc/Hz的恒定SSB相位噪声的PLL会受到该偏移频率附近的5Hz测量带宽引起的

相位波动。

相位波动。

根据频率和相位之间的基本关系,使用以下表达式从其相位噪声中获得PLL输出的频率波动(Hz):

![]() (6)

(6)

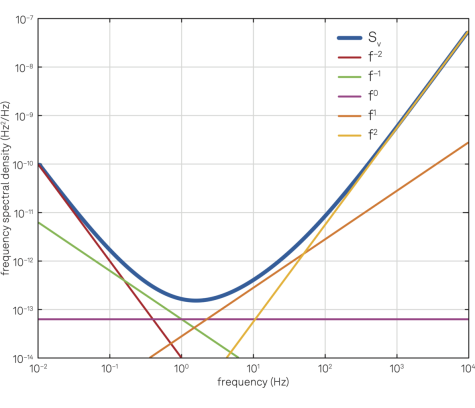

与相位噪声PSD类似,我们可以将频率噪声的功率谱密度定义为其自相关的傅立叶变换。频率噪声PSD,由Sν(f)表示,单位Hz2/Hz,并且可以使用以下等式从相位噪声PSD获得:

![]() (7)

(7)

根据应用,人们可能对相位或频率噪声感兴趣;使用公式7使得可以将一个PSD转换为另一个PSD。

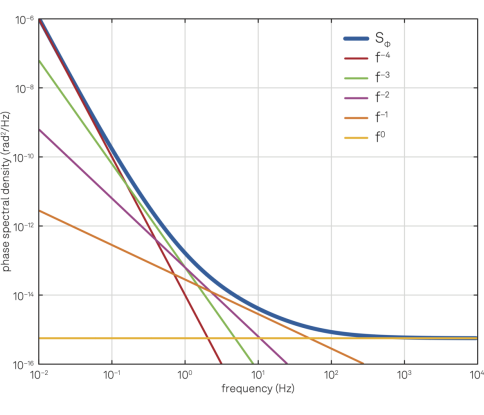

幂律

描述相位和频率噪声的功率谱密度的启发式方法是使用如下的幂律函数[11]:

![]() (8)

(8)

上述表达式中的每个项对应于不同类型或颜色的噪声。例如,b1显示了闪烁相位噪声在频谱密度中的贡献,其由−10 dB/decade的斜率确定,而b2对应于噪声频谱中斜率为−20 dB/decade的布朗相位噪声。根据等式7,频率噪声频谱可以使用幂律函数描述如下:

![]() (9)

(9)

表1示出了对PLL的总噪声频谱密度有贡献的相位和频率噪声的不同颜色。每种颜色都决定了光谱在对数刻度上的斜率。事实上,表中的项fi对应于在频谱密度中具有10i dB/decade的斜率的噪声颜色。图12和13描述了由PLL控制的振荡器的相位和频率噪声频谱。根据PLL系统的组件,噪声颜色之一可以在特定频率范围内占主导地位。这可以从该特定频率范围中的频谱曲线的斜率来理解。

例如,在图12所示的情况下,对于1 kHz以上的频率,相位噪声几乎是白色的,因为对于该频率范围,频谱曲线近似平坦。作为一种频域工具,相位噪声的幂律描述与Allan方差或Allan偏差密切相关,Allan方差是分析振荡器噪声特性的时域工具。通过测量频谱或Allan方差,我们可以很容易地获得另一个,并在时域和频域中提供相位和频率噪声的完整描述[11]。

表1:各种类型的相位和频率噪声及其对噪声频谱的贡献。

图12:相位噪声的频谱密度和不同噪声颜色的贡献。 图13:频率噪声频谱密度和不同噪声颜色的贡献。

莱森效应

谐振跟踪中的常见场景是由PLL驱动的谐振器给出的,其中其VCO的白相位噪声占主导地位。因此,我们期望f2阶的频率噪声。然而,除了这种紫色频率噪声之外,我们还看到了一个白色频率噪声项,可以用莱森效应来解释[12]。假设具有谐振频率f0 和质量因子Q的谐振器由PLL的VCO驱动。根据莱森效应,谐振器输出端的相位噪声可以由谐振器输入端的VCO相位噪声Sφ 通过以下表达式[11]获得:

其中 fL =f0/2Q 被称为莱森频率。如果VCO具有b0的白色相位噪声,则根据等式10,谐振器的相位噪声包括白色项b0和红色项b0fL2/f2。将等式7应用于谐振器相位噪声导致具有两个项的频率噪声频谱:蓝色项 b0f2和白色项b0fL2。图14显示了当谐振器由具有白色相位噪声的VCO驱动时,谐振器的相位和频率噪声的频谱。该图清楚地表明,对于高于谐振器的莱森频率(在这种情况下fL =20Hz)的频率,主要噪声来自VCO;相反,对于低于fL 的频率,谐振器对噪声频谱有贡献并改变噪声颜色。

图14:(a) 莱森频率为20 Hz的谐振器的相位噪声(蓝线)由具有白色相位噪声的受控振荡器驱动(红线)。(b) 谐振器的频率噪声。

锁相环作为相位和/或频率跟踪和同步的重要部件,广泛应用于物理、电子、光子学和通信领域。PLL包括三个主要部件:相位检测器、PID控制器和受控振荡器。这些组成模块中的每一个都有助于整个系统的整体响应。

最常见的PLL应用可以通过以下三种主要配置之一实现:频率跟踪、谐振驱动和振荡器控制。基于FPGA的模拟信号锁相环,如苏黎世仪器公司的锁相放大器提供的锁相环,提供闭环频率和相位控制,具有相位展开和自动调谐功能等集成功能,以及用户友好的工具,包括PID Advisor和参数扫描器。

参考文献

[1] Thomas H. Lee. The Design of CMOS Radio Frequency Integrated Circuits, 2nd ed. Cambridge University Press, 2003.

[2] Roland E. Best. Phase-Locked Loops. McGraw Hill, 2003.

[3] Behzad Razavi. Design of Analog CMOS Integrated Circuits. McGraw Hill, 2002.

[4] Zurich Instruments. Principles of Lock-in Detection, 2016.

[5] Zurich Instruments. Control of MEMS Coriolis Vibratory Gyroscopes, 2015.

[6] Zurich Instruments. Interferometer Stabilization with Linear Phase Control Made Easy, 2018.

[7] Donald R. Stephens. Phase-Locked Loops for Wireless Communications: Digital, Analog and Optical Implementations. Wiley, 2002.

[8] J.P. Costas. Synchronous communications. Proceedings of the IEEE, 90(8):1461–1466, 2002.

[9] Zurich Instruments. Parametric Feedback Cooling, 2014.

[10] IEEE standard definitions of physical quantities for fundamental frequency and time metrology--random instabilities. IEEE Std. Std 1139-2008, 2009.

[11] Enrico Rubiola. Phase Noise and Frequency Stability in Oscillators. Cambridge University Press, 2010.

[12] D. B. Leeson. A simple model for feedback oscillator noise. Proceedings of the IEEE, 54(2), 1966.