在PLL或VCO的Vcc上注入白噪声和CW噪声实例

摘要

使用索相科技提供的噪声源在Vcc上注入加性高斯白噪声(AWGN)和CW噪声信号,以展示PLL/VCO电路电源电压上叠加加性高斯白噪声和杂散信号的影响。

实验目的

测量噪声和杂散对PLL/VCO电路Vcc的影响

拓展应用

信号完整性、IC设计和评估工程师在电路Vcc存在噪声和杂散信号的情况下,对其IC或PCB电路的性能进行特征化和量化。应用电路和IC包括但不限于低压高速IC、PLL/VCO、ADC、DAC和Serdes。

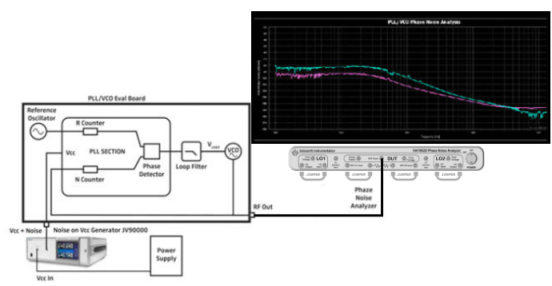

实验框图

实验步骤

1. 以0.1dB步进将AWGN和CW信号添加到供电电源线上,以模拟各种来源产生的噪声的影响,包括开关电源、地线反射、Vcc陡降以及耦合到Vcc的其他相邻电路的干扰。用户还可以确定PCB上Vcc电源线和电源电压平面的阻抗特性。

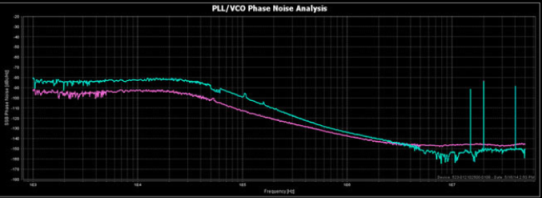

2. PLL/VCO评估板上输出由相噪分析仪监测,以测量当AWGN和/或离散CW信号注入评估板的Vcc时整体相位噪声的增加。

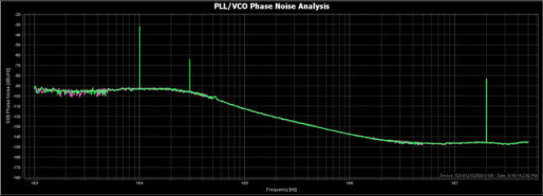

3. 通过注入宽带噪声,我们能够通过应用一个信号来测量宽带频率范围内整体相位噪声水平的增加。下图显示了相位噪声从1KHz到3MHz增加的情况。

4. 当然我们还可以在选定的频率上注入CW信号,以测量测试电路的杂散抑制情况。

索相科技提供专门用于测试需要符合特定抗干扰等级的组件,是分析电源抑制比(PSRR)的理想选择。

咨询产品信息及报价